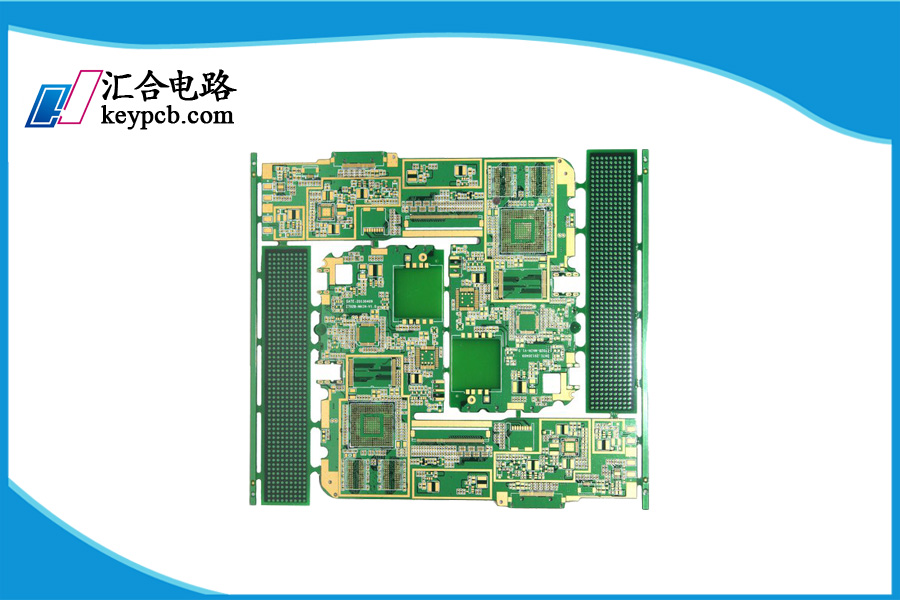

阻抗板的開發(fā)技術的標準化����、規(guī)范化與IP核的可利用性有一定關系����。傳統(tǒng)的電子設計方法至今沒有任何標準加以規(guī)范����。以單片機或DSP開發(fā)為例����,每一次新的開發(fā)����,必須選用具有更高性價比和更適合設計項目的處理器,但由于不同的處理器的結構����、語言和硬件特性有很大的差異。

?

每一次設計都必須重新學習相關的知識����,如重新了解器件的阻抗板結構和電氣特性,重新設計該處理器的功能軟件����,甚至要重新購置并了解新購置的系統(tǒng)和編譯軟件。

?

阻抗板的EDA技術則不同����,它的設計語言是標準的,不會由于設計對象的不同而改變����;它的開發(fā)工具是規(guī)范化的����,EDA軟件平臺支持任何標準化的設計語言����;它的設計成果具有通用性����,IP核具有規(guī)范的接口協(xié)議,具有良好的可移植與可測試性����。

?

適用于高效率的自頂向下設計方法。阻抗板的EDA技術的優(yōu)勢之一就是最能將所有設計環(huán)節(jié)納入統(tǒng)一的自頂向下的設計方案中����。而傳統(tǒng)的電子設計中,由于沒有規(guī)范的設計工具和表達方式����,無法進行這種先進的設計流程,只能采用自底向上的設計方法����。

?

相關閱讀:阻抗板的EDA技術設計【匯合】