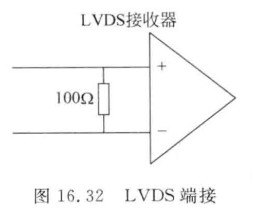

PCB快板廠家LVDS是一種低擺幅的差分信號(hào)技術(shù)��,它上面的信號(hào)可以以幾百Mbps的速率傳輸�。LVDS信號(hào)的驅(qū)動(dòng)器由一個(gè)驅(qū)動(dòng)差分線的電流源組成,通常電流為3. 5 mA���,如圖16. 32所示����。端接電阻一般跨接在正負(fù)兩路信號(hào)之間。

?

?

?

LVDS信號(hào)的接收器一般具有很高的輸入阻抗�,因此驅(qū)動(dòng)器輸出的電流大部分都流過(guò)了 lOO歐的匹配電阻,并產(chǎn)生了 350 mV的電壓�。有時(shí),為了增加抗噪聲性能��,差分線的正負(fù)兩路信號(hào)之間用2個(gè)50n的電阻串聯(lián)����,并在電阻中間連接一個(gè)濾波電容到地����。這樣,就可以減少高頻噪聲�����。隨著微電子技術(shù)的發(fā)展�,很多PCB快板廠家已經(jīng)可以把LVDS電平信號(hào)的終端電阻做到器件內(nèi)部,以減少PCB快板廠家PCB設(shè)計(jì)者的設(shè)計(jì)難度�。典型地.在Xilinx新生產(chǎn)的FPGA器件內(nèi),就將100歐的匹配電阻集成到了芯片內(nèi)部�。

?

相關(guān)閱讀:PCB快板廠家差分線的阻抗匹配【匯合】

?